Log

23.03.04 JTAG 개념 정리 초안 작성

JTAG란?

JTAG는 Joint Test Action Group의 약자로 Embedded 개발 시 사용되는 하드웨어 인터페이스 프로토콜입니다.

IEEE 1149.1 -1990로 표준이 지정되어 있습니다.

JTAG 역사

PCB보드에 부착되어 있는 칩들은 서로 수많은 wire로 연결이 되어있습니다. 이 보드를 판매하기 위해서는 칩간의 연결이 정상적으로 연결되어있는지 확인해야 할 필요가 있습니다. 한개의 wire가 제대로 연결이 되어있지 않아도 치명적일 수 있기 때문입니다. 그러나 확인해야 할 wire가 매우 많았기 때문에 일일이 손으로 확인하기엔 너무 힘든 일입니다. 따라서 이러한 경우에 물리적으로 wire가 연결이 잘 되었는지 확인하기 위해 등장한 검증기법이 "Boundary Scan" 이며 이 기법을 사용하기 위해 사용하는 인터페이스가 바로 "JTAG" 입니다.

# Boundary Scan 동작원리

http://forum.falinux.com/zbxe/index.php?document_srl=405972&mid=lecture_tip

JTAG 사용처

JTAG는 FPGA(Field Programmable Gate Array)와 ASIC(Application Specific Integrated Circuit), 마이크로 프로세서(ex. STM32)에 사용됩니다. 이 인터페이스를 통해 보드의 내부 레지스터 값을 보거나 펌웨어 reflash를 수행함으로써 디버깅을 수행할 수 있습니다.

JTAG 인터페이스

그림 1 출처 : https://kkhipp.tistory.com/186

JTAG란?

우선 위키백과에 설명이 잘 되어있어 정리하겠습니다. JTAG(Joint Test Action Group)으로 디지털 회로에서 특정 노드의 디지털 입출력을 위해 직렬 통신 방식으로 출력 데이터를 전송하거나 입력데이

kkhipp.tistory.com

JTAG를 사용할때 주로 사용하는 포트는 아래와 같습니다.

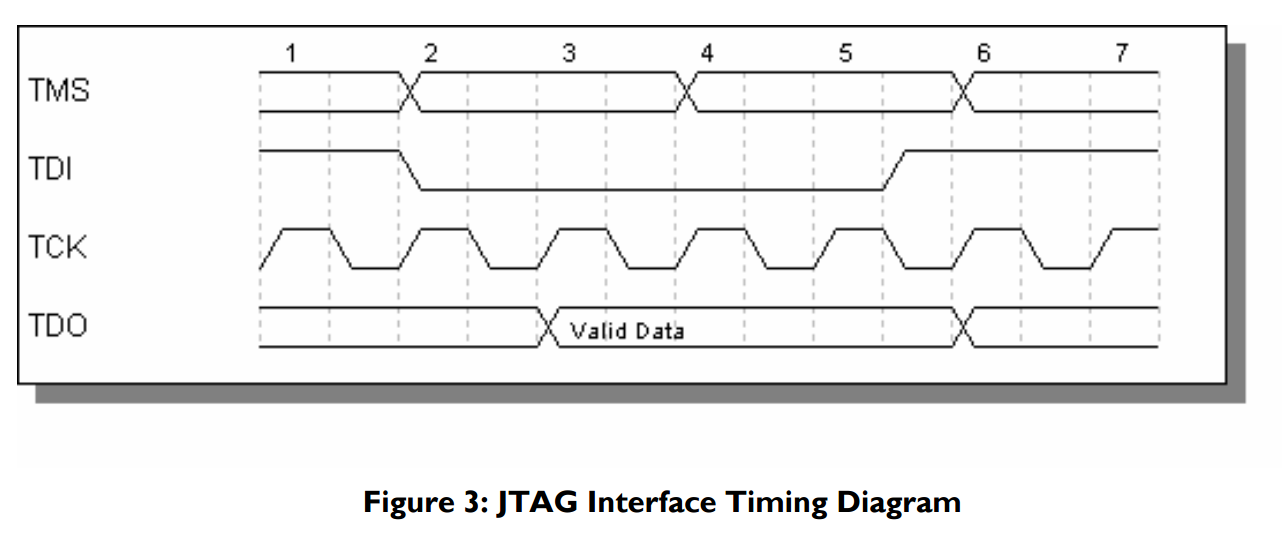

- TCLK(Test Clock) : 테스트를 위한 Clock. TDI,TDO,TMS는 이 Clock에 동기화되어 사용됩니다. (보통 TCLK는 posedge로 사용됩니다.)[1]

- TRST(Test Reset) : 테스트를 위한 리셋신호. 전원 인가 시 TAP을 초기화 한다. JTAG의 추가 기능이기 떄문에 본인이 사용하는 JTAG 인터페이스에 없을 수도 있습니다.

- TDI(Test Data Input) : 테스트 데이터 입력

- TDO(Test Data Output) : 테스트 데이터 출력

- TMS(Test Mode Select) : 테스트 모드로 전환하기 위한 제어 신호

위 5개의 포트를 TAP(Test Access Port)라고 합니다.

그림 2 출처 : https://www.cnblogs.com/shangdawei/p/4753682.html

JTAG – A technical overview and Timing - IAmAProgrammer - 博客园

This document provides you with interesting background information about the technology that underpi

www.cnblogs.com

# TMS 부가 설명

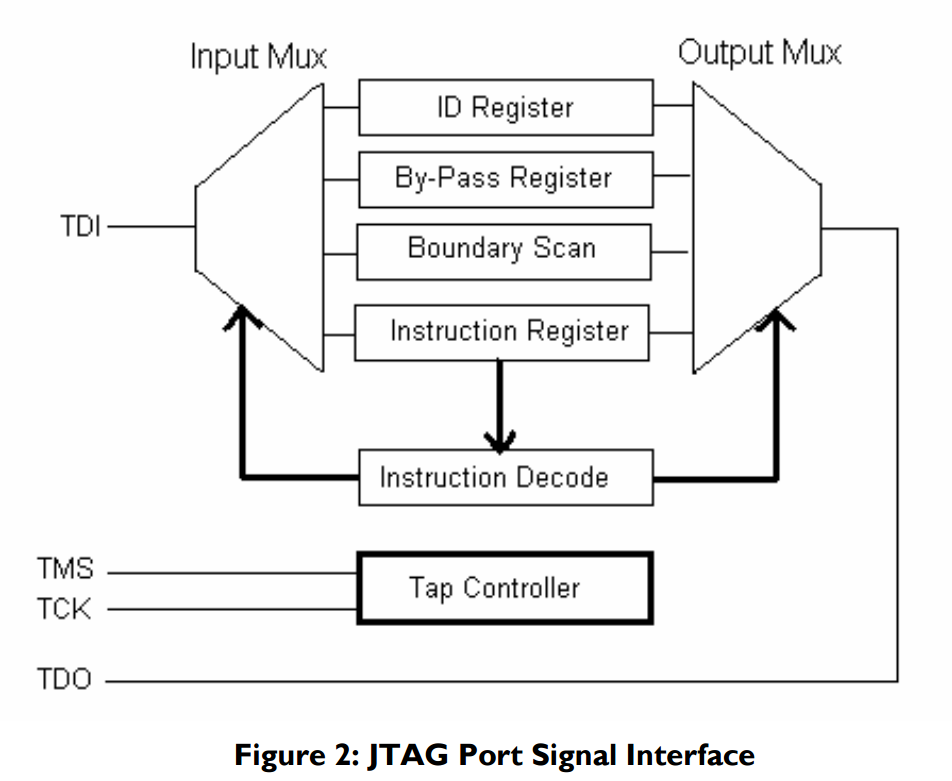

JTAG가 지원되는 IC들은 내부에 TAP Controller를 포함하고 있습니다. 이 TAP Controller는 16개의 state machine을 가지고 있고 TMS에 의해 제어됩니다. 이 TMS는 각 IC들의 TAP Controller들과 병렬적으로 연결되어 있기 때문에 모든 TAP Controller들은 같은 State를 가지게 됩니다. [1]

TAP Controller는 TAP을 통해 내부 회로에 엑세스 할 수 있습니다.

그림 3 출처 : https://www.fpga4fun.com/JTAG2.html

fpga4fun.com - JTAG 2 - How JTAG works

☰ JTAG 2 - How JTAG works Now that we know how to connect JTAG to different ICs, let's see in details how JTAG works and how to control it from a PC. Control JTAG from your PC You use a "JTAG cable" to control a JTAG bus from a PC. The JTAG cable is just

www.fpga4fun.com

이 TAP Controller에 대한 자세한 내용은 그림 3 출처에 있습니다.

JTAG Hardware 구조

그림 3 출처 : https://ko.wikipedia.org/wiki/JTAG

JTAG - 위키백과, 우리 모두의 백과사전

위키백과, 우리 모두의 백과사전. JTAG(Joint Test Action Group)은 디지털 회로에서 특정 노드의 디지털 입출력을 위해 직렬 통신 방식으로 출력 데이터를 전송하거나 입력데이터를 수신하는 방식을 말

ko.wikipedia.org

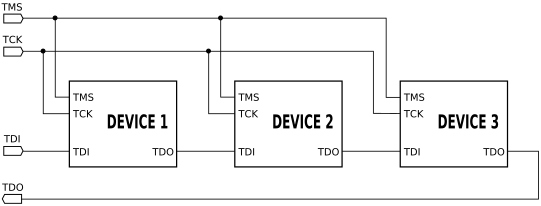

그림 3에서 보이는 것과 같이 JTAG 신호들은 데이지 체인(Daisy-chained) : 연속적인 Device의 연결) 형식으로 연결되어 있다.[2] Device 1의 TDO가 Device2의 TDI로 입력되는 것처럼 Device들끼리 연속적으로 이어져 있는것을 알 수 있다.

(그림 3은 TRST가 포함되지 않았다.)

그림 4,5 출처 : https://www.cnblogs.com/shangdawei/p/4753682.html

JTAG – A technical overview and Timing - IAmAProgrammer - 博客园

This document provides you with interesting background information about the technology that underpi

www.cnblogs.com

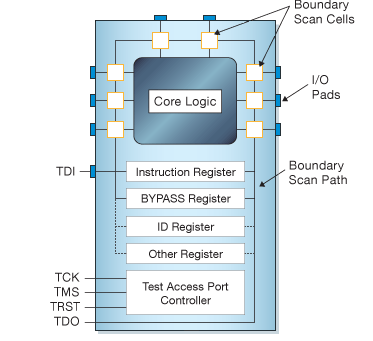

JTAG에 사용되는 Boundary Scan Cell은 디바이스의 입출력 단에만 존재한다.[3]

JTAG의 동작 방식

칩 내부에 Boundary Logic Cell을 만들고 외부 pin과 1대1로 연결되어 프로세서가 할 수 있는 동작을 중간에 Cell을 통해 인위적으로 수행하게 한다.

JTAG는 Serial 방식으로 동작하며 속도는 10 ~ 100MHz로 동작한다.

Reference

[1] https://www.fpga4fun.com/JTAG2.html

fpga4fun.com - JTAG 2 - How JTAG works

☰ JTAG 2 - How JTAG works Now that we know how to connect JTAG to different ICs, let's see in details how JTAG works and how to control it from a PC. Control JTAG from your PC You use a "JTAG cable" to control a JTAG bus from a PC. The JTAG cable is just

www.fpga4fun.com

[2] https://m.blog.naver.com/yhol98/221702590182

JTAG, J-LINK 란 무엇인가?

안녕하세요 HeStory 입니다. Firmware를 간만에 다시 보기 위해 이것저것 알아보는 중 예전에 자주 사용...

blog.naver.com

[3] https://yebig.tistory.com/16?category=58805

JTAG의 소개 및 원리 2편

JTAG의 소개 및 원리 2편 등록: 2001-07-25 15:01:03 1 탄에서 소개한대로 JTAG이 만들어 진 이유는 조금 아셨을 겁니다. 자자 이전 편에서 Boundary-Scan Cell 이라는 것이 생겼습니다. 하지만 이것은 아직 완

yebig.tistory.com

본 게시물은 앞으로 수정하면서 부족한 부분을 채워갈 예정입니다.

잘못된 정보나 추가로 필요한 정보가 있다면 댓글로 남겨주시기 바랍니다.